华南理工大学学报(自然科学版) ›› 2023, Vol. 51 ›› Issue (5): 95-103.doi: 10.12141/j.issn.1000-565X.220612

所属专题: 2023年电子、通信与自动控制

HEVC帧内率失真优化预测模式的并行流水线硬件设计

林志坚 丁永强 杨秀芝 吴林煌

- 福州大学 物理与信息工程学院,福建 福州 350108

Parallel Pipeline Hardware Design of Intra Rate-Distortion Optimization Prediction Mode in HEVC

LIN Zhijian DING Yongqiang YANG Xiuzhi WU Linhuang

- College of Physics and Information Engineering,Fuzhou University,Fuzhou 350108,Fujian,China

摘要:

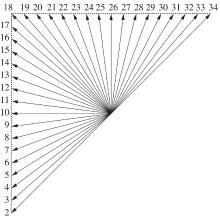

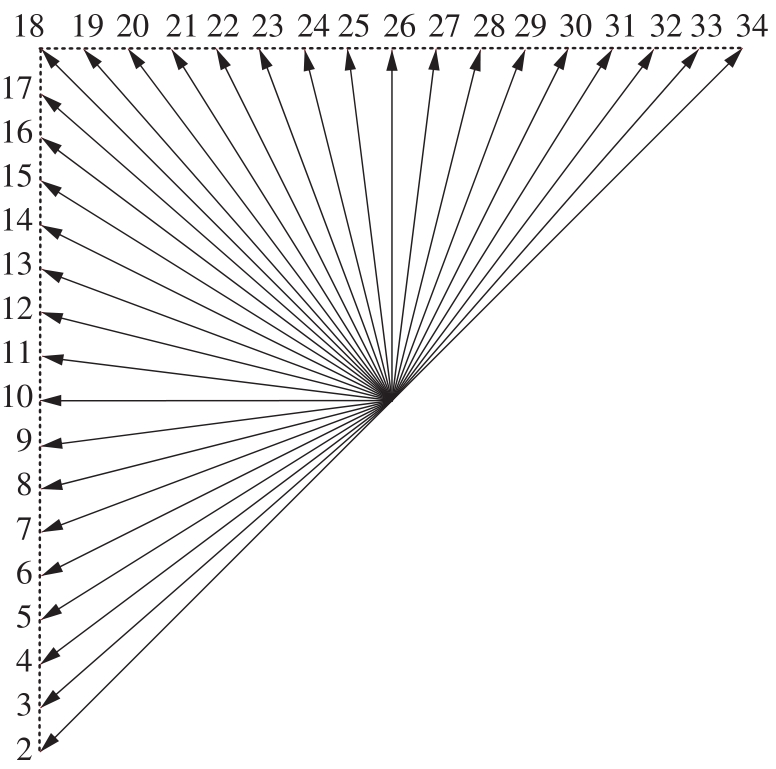

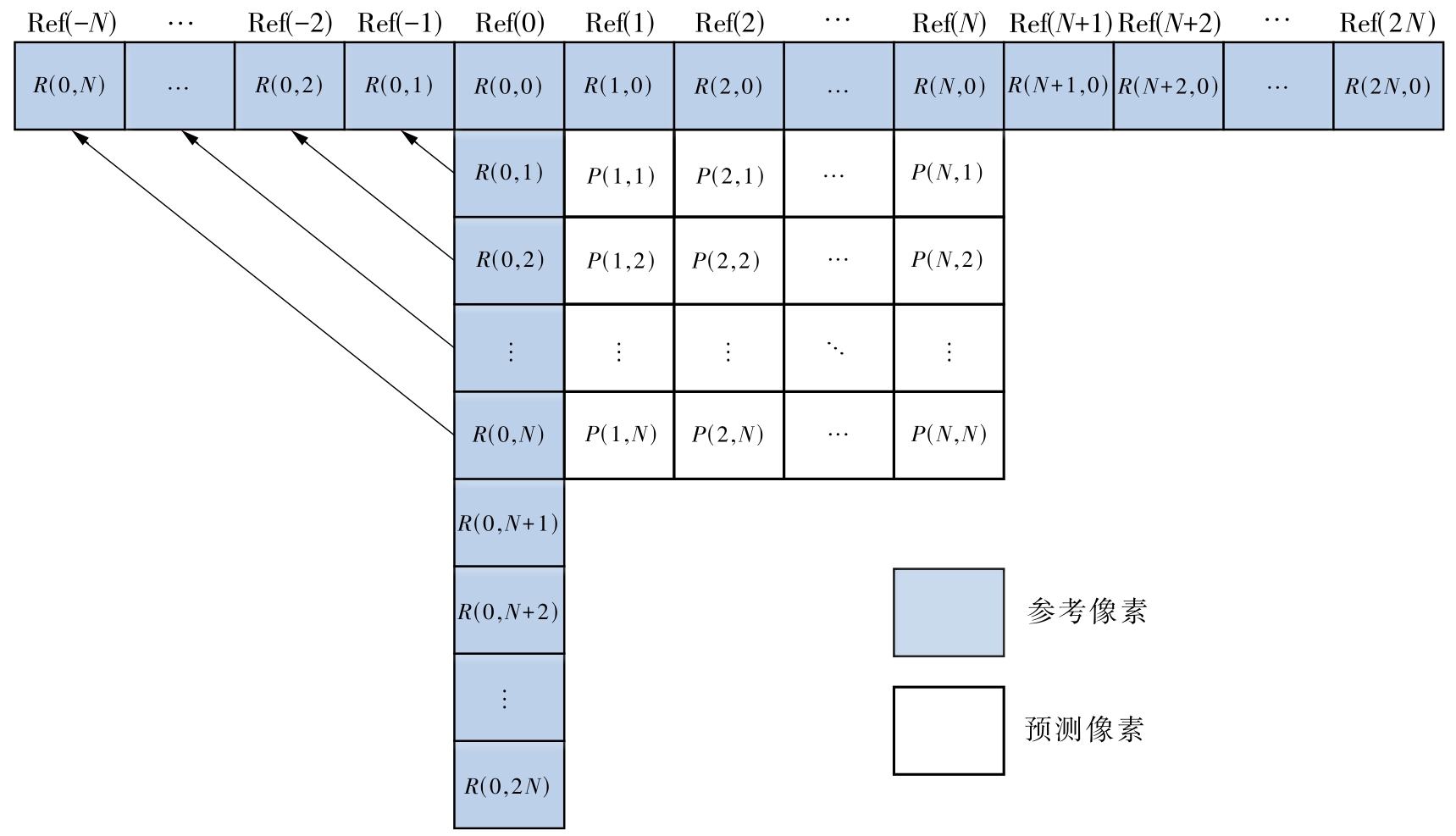

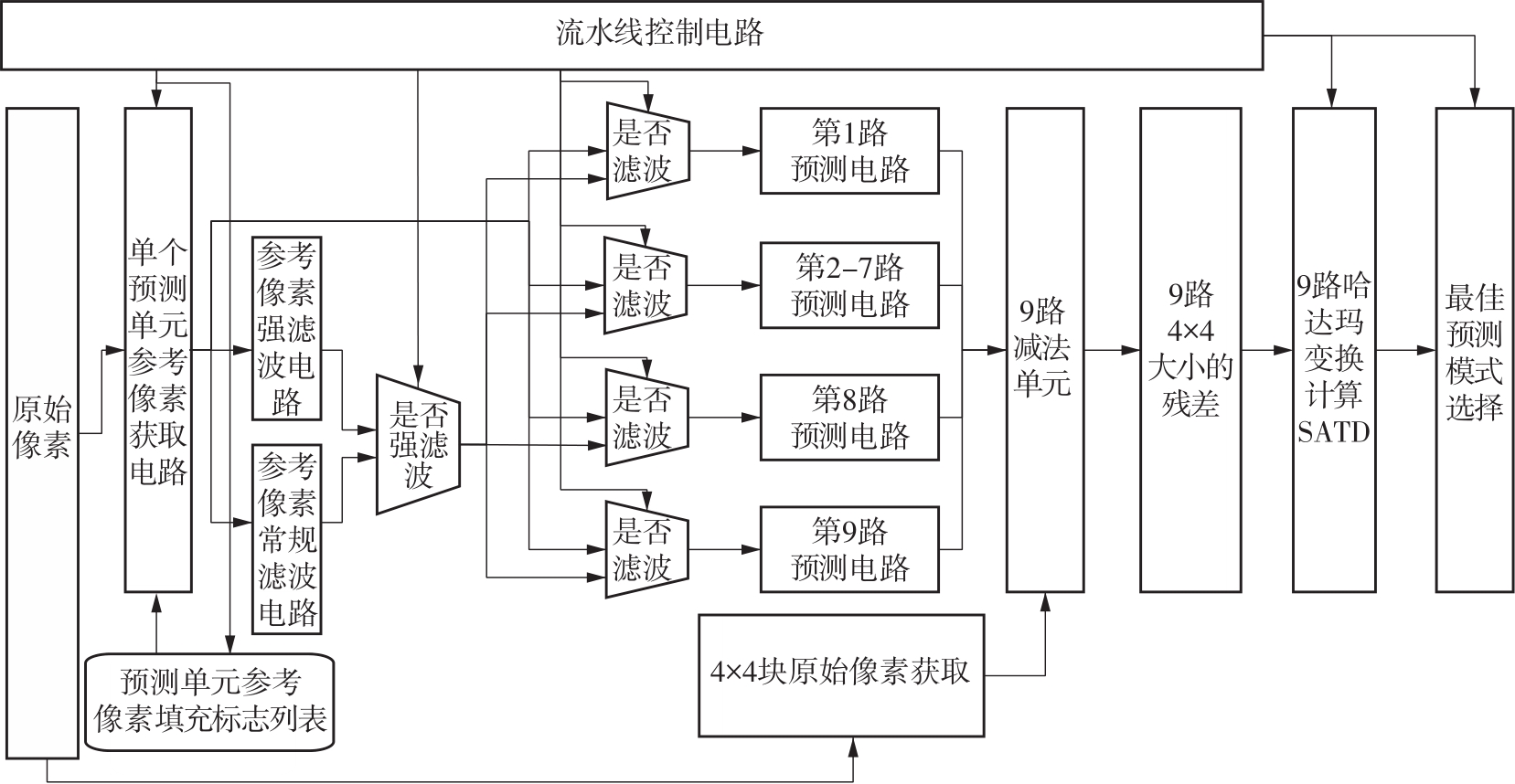

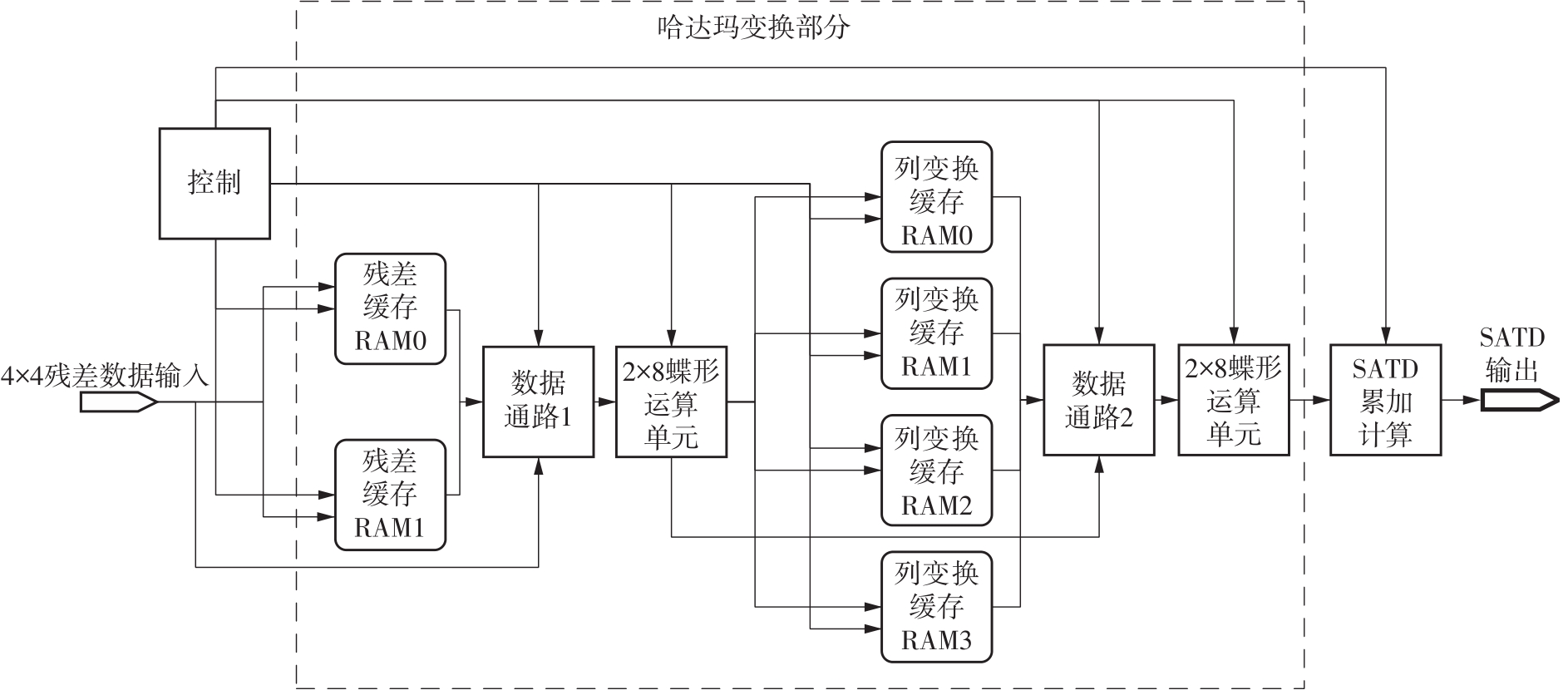

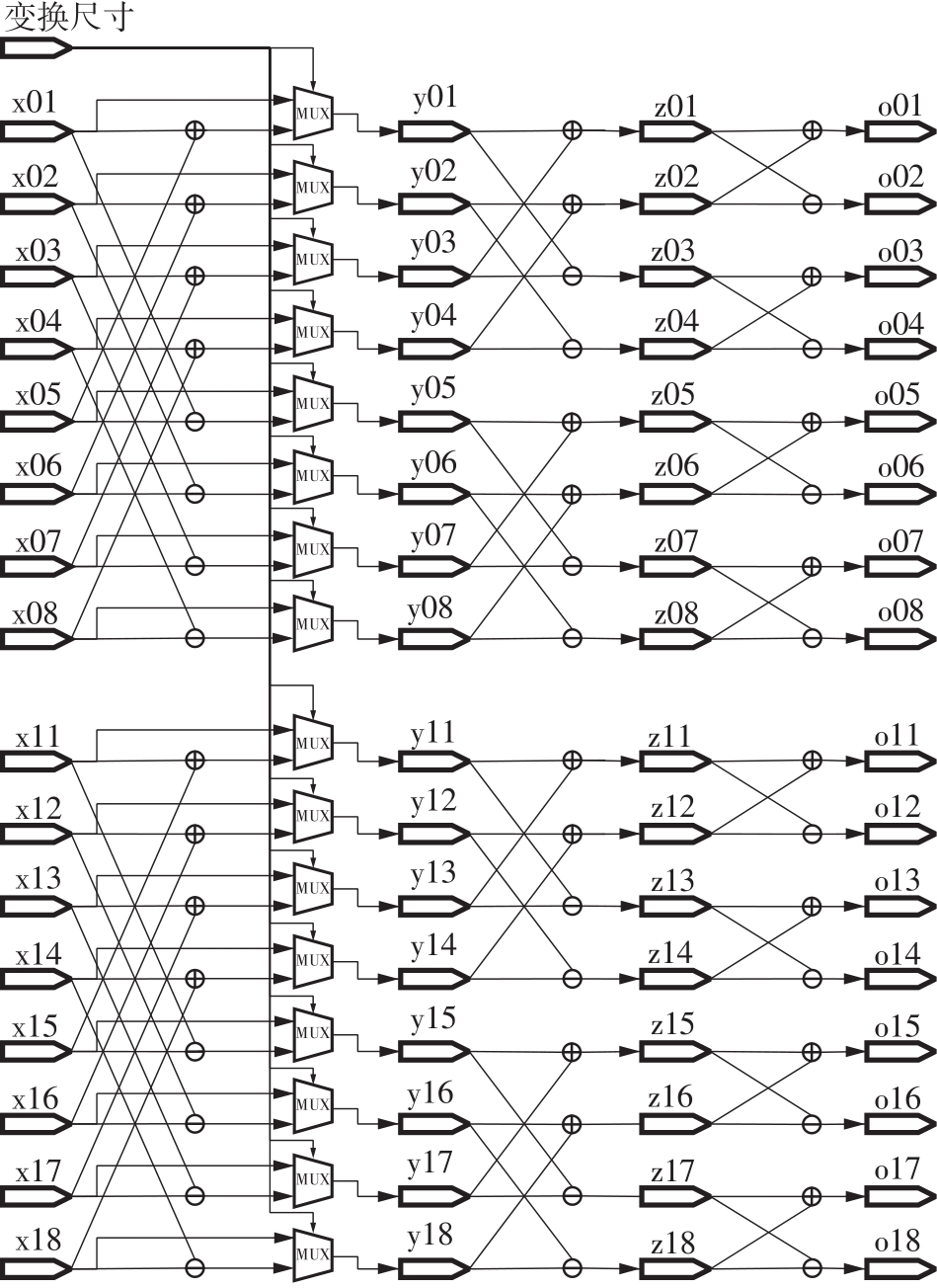

近年来,随着人们对视频数据需求的不断增加,视频的分辨率和帧率也在不断地提高,而实时视频序列的压缩编码速度往往受到帧率和分辨率的影响,分辨率和帧率越大,编码所需要的时间越长。为了实现更高分辨率和更高帧率的视频序列实时压缩编码,文中设计了一种新的帧内率失真优化预测模式的并行流水线硬件架构,该架构支持最大64×64编码树单元的帧内预测编码。首先设计了9路预测模式并行方案;然后,按照Z型扫描顺序实现以4×4块为基本处理单元的流水线硬件架构,并复用32×32预测单元的预测数据,用以代替64×64预测单元的预测数据,减少运算量;最后,基于该流水线架构,提出了一种新的哈达玛变换电路,用以实现高效的流水线处理。实验结果表明:在Altera Arria 10系列的现场可编程门阵列上,该9路模式并行架构仅占用75 kb的查找表和55 kb的寄存器资源,主频可以达到207 MHz,完成一个64×64编码树单元的预测仅需要4 096个时钟周期,最大能够支持1 080 P分辨率99 f/s全I帧的实时编码;与已有设计方案相比,文中方案能够用更小的电路面积实现更高帧率的1 080 P实时视频编码。

中图分类号: