Journal of South China University of Technology(Natural Science) >

Hardware Acceleration Design of HEVC Entropy Encoding Syntax Elements Based on FPGA

Received date: 2022-06-06

Online published: 2023-03-07

Supported by

the National Natural Science Foundation of China(61871132);the Natural Science Foundation of Fujian Province(2020J01466)

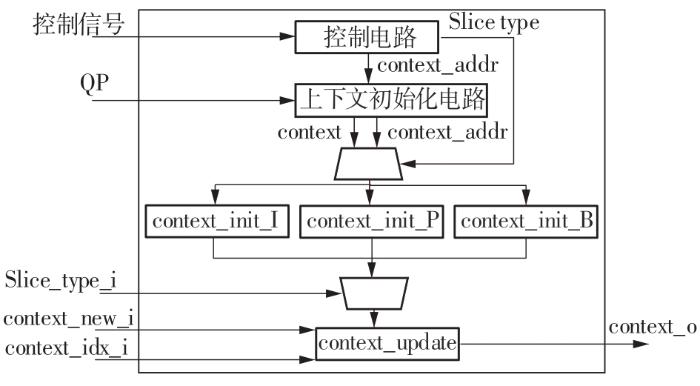

High Efficiency Video Coding (HEVC/H.265) is a widely used video coding standard in the international market. As the core encoding method of HEVC video encoding, Context Adaptive Binary Arithmetic Coding (CABAC) can improve the compression efficiency of arithmetic coding by establishing a more accurate probability model. Moreover, HEVC defines a larger variety of syntax elements and establishes more complex coding structures, further reducing information redundancy and thus reducing the bit rate. However, as the input data to CABAC, syntax elements’ high complexity of preprocessing process increases the difficulty of hardware parallel processing. As a result, the throughput rate of entropy coding hardware is difficult to improve, which becomes one of the bottlenecks for HEVC encoder to achieve higher resolution real-time coding. To further speed up the entropy encoding modules, this study designed a high-throughput CABAC entropy encoding architecture based on FPGA. Within the architecture, the pre-header information coding, pre-initialization and coding unit (CU) are able to accelerate the generation of syntax elements, which is dedicated to CABAC. Due to the scheme of efficient residual coding and partial context index pipeline computing, the reduction of path latency and the improvement of operating frequency can be achieved as well as high throughput. In this study, the proposed design, which is synthesized by using a 90 nm standard cell library, occupies a total of 2.099×104 logic gates and operates in the frequency of 200 MHz. This paper also simulated the video sequence provided by HEVC official, and counted the time required for encoding a coding tree unit (CTU) under different quantitative parameters (QP). The experimental statistics show that the time of encoding a CTU was saved by 38.2% on average.

Key words: entropy encoding; CABAC; FPGA; throughput rate; syntax element

LIN Zhijian, HUANG Ping, ZHENG Mingkui, et al . Hardware Acceleration Design of HEVC Entropy Encoding Syntax Elements Based on FPGA[J]. Journal of South China University of Technology(Natural Science), 2023 , 51(8) : 110 -117 . DOI: 10.12141/j.issn.1000-565X.220350

| 1 | SULLIVAN G J, OHM J R, HAN W J,et al .Overview of the high efficiency video coding (HEVC) standard[J].IEEE Transactions on Circuits and Systems for Video Technology,2012,22(12):1649-1668. |

| 2 | CAI Y, FAN Y, HUANG L,et al .A fast CABAC hardware design for accelerating the rate estimation in HEVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2022,32(4):2385-2395. |

| 3 | ONISHI T, SANO T, NISHIDA Y,et al .A single-chip 4K 60-fps 4:2:2 HEVC video encoder LSI employing efficient motion estimation and mode decision framework with scalability to 8K[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2018,26(10):1930-1938. |

| 4 | BOSSEN F, BROSS B, SUHRING K,et al .HEVC complexity and implementation analysis[J].IEEE Tran-sactions on Circuits and Systems for Video Technology,2012,22(12):1685-1696. |

| 5 | 周小朋,梁峰,李冰 .高吞吐率的高效视频编码熵编码并行硬件架构设计[J].西安交通大学学报,2020,54(7):180-186. |

| ZHOU Xiaopeng, LIANG Feng, LI Bing .High throughput rate of efficient video encoding entropy encoding parallel hardware architecture design[J].Journal of Xi’an Jiaotong University,2020,54(7):180-186. | |

| 6 | ZHOU D, ZHOU J, WEI F,et al .Ultra-high-throughput VLSI architecture of H.265/HEVC CABAC encoder for UHDTV applications[J].IEEE Transactions on Circuits and Systems for Video Technology,2015,25(3):497-507. |

| 7 | RAMOS F, SAGGIORATO A, ZATT B,et al .Residual syntax elements analysis and design targeting high-throughput HEVC CABAC[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2019,67(2):475-488. |

| 8 | 卓德珊,傅晨,冯冠雄 .一种低延迟的HEVC熵编码方法设计[J].广播电视网络,2020,27(3):101-106. |

| ZHUO Deshan, FU Chen, FENG Guanxiong .A low-latency HEVC entropy encoding method design[J].Broadcast Television Networks,2020,27(3):101-106. | |

| 9 | 郭勇,王桂海,范益波,等 .基于HEVC标准的全高清CABAC编码器设计[J].电视技术,2014,38(9):71-74. |

| GUO Yong, WANG Guihai, FAN Yibo,et al .Full HD CABAC encoder design based on HEVC standard[J].Video Engineering,2014,38(9):71-74. | |

| 10 | 万帅,杨付正 .新一代高效视频编码H.265/HEVC:原理、标准与实现[M].北京:电子工业出版社,2014. |

| 11 | MENASRI W, SKOUDARLI A, BELHADJ A,et al .Field programmable gate array implementation of variable-bins high efficiency video coding CABAC decoder with path delay optimisation[J].IET Image Processing,2019,13(6):954-963. |

| 12 | MENASRI W, MEDDAH K .Low level syntax elements study in intra Hevc/H.265 video codec[C]∥ Proceedings of the 7th International Conference on Image and Signal Processing and Their Applications.Chengdu:IEEE,2022:1-7. |

| 13 | 王一涛 .H.265/HEVC CABAC熵编码的研究与硬件实现[D].福州:福州大学,2019. |

| 14 | STANKOWSKI J, KARWOWSKI D, GRAJEK T,et al .Bitrate distribution of syntax elements in the HEVC encoded video[C]∥ Proceedings of the 2014 International Conference on Signals and Electronic Systems.Poznan:IEEE,2014:1-4. |

| 15 | KIM D, MOON J, LEE S .Hardware implementation of HEVC CABAC encoder[C]∥ Proceedings of the International SoC Design Conference.New York:IEEE,2015:183-184. |

| 16 | PENG B, DING D, ZHU X,et al .A hardware CABAC encoder for HEVC[C]∥ Proceedings of the IEEE International Symposium on Circuits and Systems.New York:IEEE,2013:1372-1375. |

/

| 〈 |

|

〉 |