Journal of South China University of Technology(Natural Science) >

Parallel Pipeline Hardware Design of Intra Rate-Distortion Optimization Prediction Mode in HEVC

Received date: 2022-09-20

Online published: 2023-01-13

Supported by

the General Program of the National Natural Science Foundation of China(61871132)

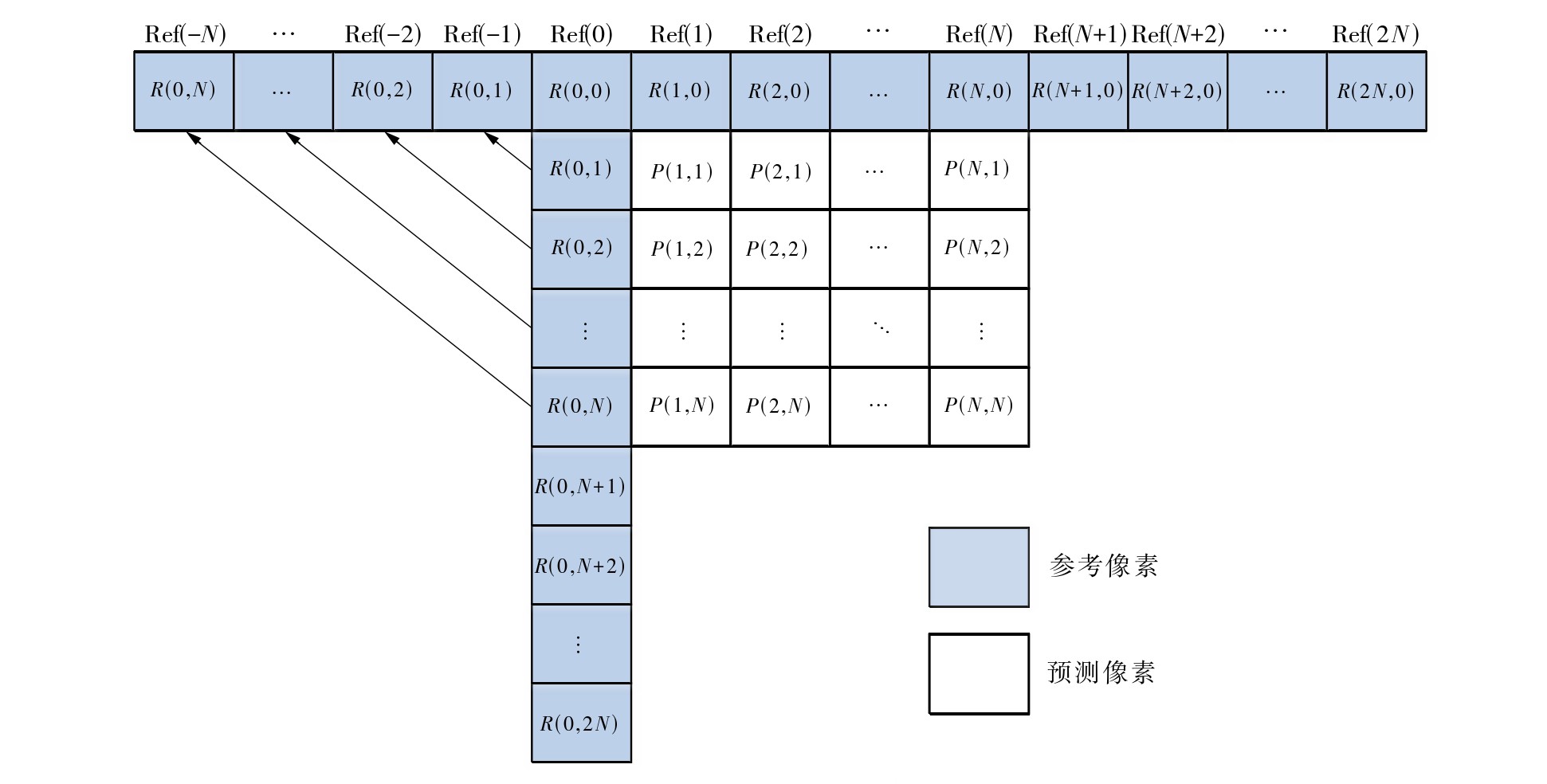

In recent years, the resolution and frame rate of video have been continuously improved to meet people’s increasing demand for video data. However, the compression encoding speed of real-time video sequence is often restricted by frame rate and resolution. The higher the frame rate and resolution are, the longer the encoding time will be. In order to achieve real-time compression encode for video sequences with higher resolution and frame rate, this paper designed a new parallel pipeline hardware architecture of intra rate-distortion optimization prediction mode, which supports intra prediction coding of up to 64×64 coding tree unit. Firstly, a parallel scheme with 9-way prediction mode was designed. Secondly, a pipeline hardware architecture was implemented based on a 4×4 block as the basic processing unit in a Z-shaped scanning order, and the prediction data of 32×32 prediction units were reused to replace the prediction data of 64×64 prediction units so as to reduce the amount of calculation. Lastly, a new Hadamard transform circuit was proposed based on this pipelined architecture for efficient pipelined processing. The experimental results show that: on the Altera Arria 10 series field programmable gate array, the 9-way mode parallel architecture only occupies 75 kb look up table and 55 kb register resources, the main frequency can reach 207 MHz, and it only takes 4 096 clocks cycles to complete a 64×64 coding tree unit prediction and can support real-time encoding of 1 080 P resolution 99 f/s full I-frame at most. Compared with the existing design scheme, the scheme designed in this paper can realize higher frame rate 1 080 P real time video encoding with smaller circuit area.

LIN Zhijian, DING Yongqiang, YANG Xiuzhi, et al . Parallel Pipeline Hardware Design of Intra Rate-Distortion Optimization Prediction Mode in HEVC[J]. Journal of South China University of Technology(Natural Science), 2023 , 51(5) : 95 -103 . DOI: 10.12141/j.issn.1000-565X.220612

| 1 | 胡永健,龚文斌,刘琲贝,等 .修改标志位的大容量无损HEVC信息隐藏方法[J].华南理工大学学报(自然科学版),2018,46(5):1-8. |

| HU Yongjian, GONG Wenbin, LIU Beibei,et al .Large-capacity lossless HEVC information hiding method by modifying flag bits [J].Journal of South China University of Technology (Natural Science Edition),2018,46(5):1-8. | |

| 2 | 朱秀昌,李欣,陈杰 .新一代视频编码标准:HEVC[J].南京邮电大学学报(自然科学版),2013,33(3):1-11. |

| ZHU Xiuchang, LI Xin, CHEN Jie .New generation of video encoding standards:HEVC[J].Journal of Nanjing University of Posts and Telecommunications (Natural Science Edition),2013,33(3):1-11. | |

| 3 | KIM Y, JUN D S, JUNG S,et al .A fast intra-prediction method in HEVC using rate-distortion estimation based on Hadamard transform[J].ETRI Journal,2013,35(2):270-280. |

| 4 | KALALI E, HAMZAOGLU I .An approximate HEVC intra angular prediction hardware[J].IEEE Access,2019,8:2599-2607. |

| 5 | SHEN W, FAN Y, HUANG L,et al .A hardware-friendly method for rate-distortion optimization of HEVC intra coding[C]∥ Proceedings of 2014 International Symposium on VLSI Design,Automation and Test.Hsinchu:IEEE,2014:1-4. |

| 6 | XU Y, HUANG X .Hardware-oriented fast CU size and prediction mode decision algorithm for HEVC intra prediction[C]∥ Proceedings of 2019 IEEE the 5th International Conference for Convergence in Technology.Bombay:IEEE,2019:1-5. |

| 7 | ZHANG Y, LU C .Efficient algorithm adaptations and fully parallel hardware architecture of H.265/HEVC intra encoder[J].IEEE Transactions on Circuits and Systems for Video Technology,2018,29(11):3415-3429. |

| 8 | 杨贺,杨秀芝,陈建 .一种新的基于FPGA的HEVC帧内预测硬件结构[J].福州大学学报(自然科学版),2020,48(3):318-324. |

| YANG He, YANG Xiuzhi, CHEN Jian .A new hardware structure of HEVC intra prediction based on FPGA [J].Journal of Fuzhou University(Natural Science Edition),2020,48(3):318-324. | |

| 9 | MIN B, XU Z, CHEUNG R C C .A fully pipelined hardware architecture for intra prediction of HEVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2016,27(12):2702-2713. |

| 10 | LU W, YU N,NAN J,et al .A hardware structure of HEVC intra prediction[C]∥ Proceedings of 2015 the 2nd International Conference on Information Science and Control Engineering.Shanghai:IEEE,2015:555-559. |

| 11 | CHEN W, HE Q, LI S,et al .Parallel implementation of H.265 intra-frame coding based on FPGA heterogeneous platform[C]∥ Proceedings of 2020 IEEE the 22nd International Conference on High Performance Computing and Communications;IEEE the 18th International Conference on Smart City;IEEE the 6th International Conference on Data Science and Systems. Yanuca Island:IEEE,2020:736-743. |

| 12 | WANG M, WEI H, FANG Y,et al .Fast mode selection algorithm for HEVC intra encoder[C]∥ Proceedings of 2018 IEEE International Conference on Automation,Electronics and Electrical Engineering.Shenyang:IEEE,2018:169-172. |

| 13 | TARIQ J, IJAZ A, ARMGHAN A,et al .HEVC’s intra mode process expedited using Histogram of oriented gradients[J].Journal of Visual Communication and Image Representation,2022,88:103594/1-10. |

| 14 | 杨秀芝,赵敏,施隆照,等 .面向硬件的帧内预测模式选择快速算法与实现[J].计算机辅助设计与图形学学报,2019,31(1):158-164. |

| YANG Xiuzhi, ZHAO Min, SHI Longzhao,et al .Research and implementation of fast algorithm for intra prediction mode selection oriented to hardware[J].Journal of Computer-Aided Design & Computer Graphics,2019,31(1):158-164. | |

| 15 | ATAPATTU S, LIYANAGE N, MENUKA N,et al .Real time all intra HEVC HD encoder on FPGA[C]∥ Proceedings of 2016 IEEE the 27th International Conference on Application-specific Systems,Architectures and Processors.London:IEEE,2016:191-195. |

| 16 | AMISH F, BOURENNANE E .Fully pipelined real time hardware solution for high efficiency video coding (HEVC) intra prediction[J].Journal of Systems Architecture,2016,64:133-147. |

/

| 〈 |

|

〉 |