收稿日期: 2022-09-20

网络出版日期: 2023-01-13

基金资助

国家自然科学基金面上项目(61871132);福建省高等学校科技创新团队项目(500190)

Parallel Pipeline Hardware Design of Intra Rate-Distortion Optimization Prediction Mode in HEVC

Received date: 2022-09-20

Online published: 2023-01-13

Supported by

the General Program of the National Natural Science Foundation of China(61871132)

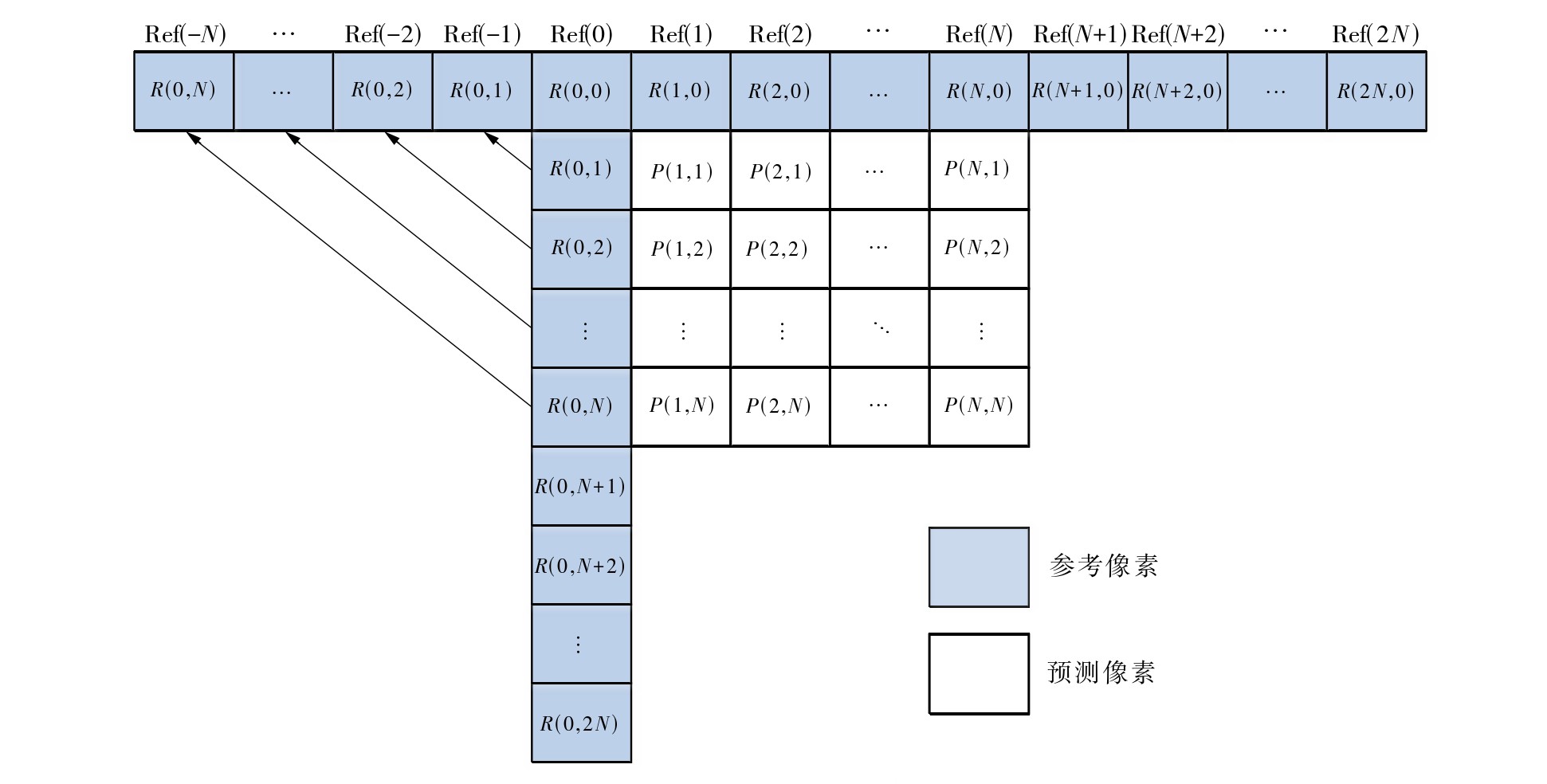

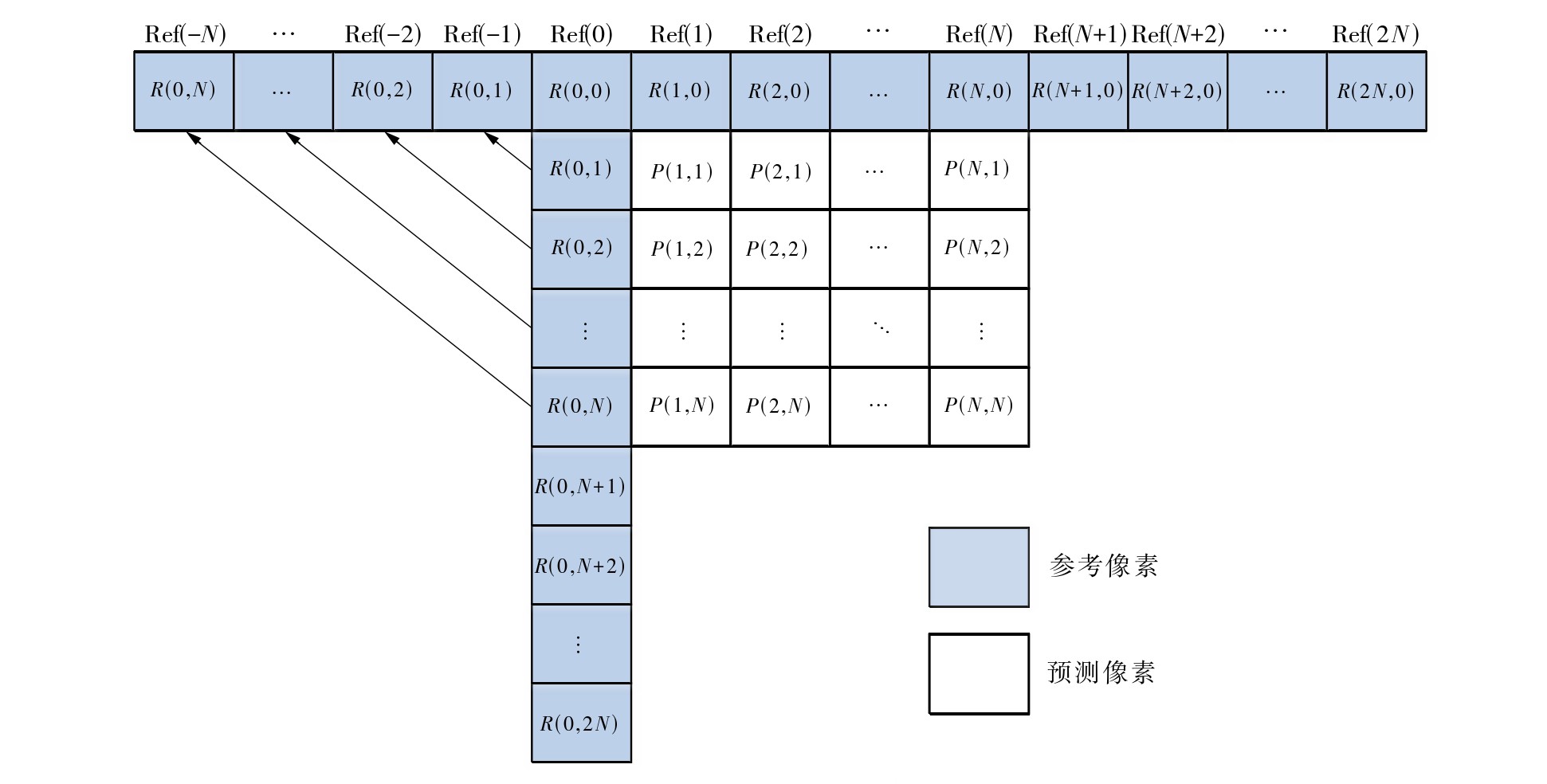

近年来,随着人们对视频数据需求的不断增加,视频的分辨率和帧率也在不断地提高,而实时视频序列的压缩编码速度往往受到帧率和分辨率的影响,分辨率和帧率越大,编码所需要的时间越长。为了实现更高分辨率和更高帧率的视频序列实时压缩编码,文中设计了一种新的帧内率失真优化预测模式的并行流水线硬件架构,该架构支持最大64×64编码树单元的帧内预测编码。首先设计了9路预测模式并行方案;然后,按照Z型扫描顺序实现以4×4块为基本处理单元的流水线硬件架构,并复用32×32预测单元的预测数据,用以代替64×64预测单元的预测数据,减少运算量;最后,基于该流水线架构,提出了一种新的哈达玛变换电路,用以实现高效的流水线处理。实验结果表明:在Altera Arria 10系列的现场可编程门阵列上,该9路模式并行架构仅占用75 kb的查找表和55 kb的寄存器资源,主频可以达到207 MHz,完成一个64×64编码树单元的预测仅需要4 096个时钟周期,最大能够支持1 080 P分辨率99 f/s全I帧的实时编码;与已有设计方案相比,文中方案能够用更小的电路面积实现更高帧率的1 080 P实时视频编码。

林志坚, 丁永强, 杨秀芝, 等 . HEVC帧内率失真优化预测模式的并行流水线硬件设计[J]. 华南理工大学学报(自然科学版), 2023 , 51(5) : 95 -103 . DOI: 10.12141/j.issn.1000-565X.220612

In recent years, the resolution and frame rate of video have been continuously improved to meet people’s increasing demand for video data. However, the compression encoding speed of real-time video sequence is often restricted by frame rate and resolution. The higher the frame rate and resolution are, the longer the encoding time will be. In order to achieve real-time compression encode for video sequences with higher resolution and frame rate, this paper designed a new parallel pipeline hardware architecture of intra rate-distortion optimization prediction mode, which supports intra prediction coding of up to 64×64 coding tree unit. Firstly, a parallel scheme with 9-way prediction mode was designed. Secondly, a pipeline hardware architecture was implemented based on a 4×4 block as the basic processing unit in a Z-shaped scanning order, and the prediction data of 32×32 prediction units were reused to replace the prediction data of 64×64 prediction units so as to reduce the amount of calculation. Lastly, a new Hadamard transform circuit was proposed based on this pipelined architecture for efficient pipelined processing. The experimental results show that: on the Altera Arria 10 series field programmable gate array, the 9-way mode parallel architecture only occupies 75 kb look up table and 55 kb register resources, the main frequency can reach 207 MHz, and it only takes 4 096 clocks cycles to complete a 64×64 coding tree unit prediction and can support real-time encoding of 1 080 P resolution 99 f/s full I-frame at most. Compared with the existing design scheme, the scheme designed in this paper can realize higher frame rate 1 080 P real time video encoding with smaller circuit area.

| 1 | 胡永健,龚文斌,刘琲贝,等 .修改标志位的大容量无损HEVC信息隐藏方法[J].华南理工大学学报(自然科学版),2018,46(5):1-8. |

| HU Yongjian, GONG Wenbin, LIU Beibei,et al .Large-capacity lossless HEVC information hiding method by modifying flag bits [J].Journal of South China University of Technology (Natural Science Edition),2018,46(5):1-8. | |

| 2 | 朱秀昌,李欣,陈杰 .新一代视频编码标准:HEVC[J].南京邮电大学学报(自然科学版),2013,33(3):1-11. |

| ZHU Xiuchang, LI Xin, CHEN Jie .New generation of video encoding standards:HEVC[J].Journal of Nanjing University of Posts and Telecommunications (Natural Science Edition),2013,33(3):1-11. | |

| 3 | KIM Y, JUN D S, JUNG S,et al .A fast intra-prediction method in HEVC using rate-distortion estimation based on Hadamard transform[J].ETRI Journal,2013,35(2):270-280. |

| 4 | KALALI E, HAMZAOGLU I .An approximate HEVC intra angular prediction hardware[J].IEEE Access,2019,8:2599-2607. |

| 5 | SHEN W, FAN Y, HUANG L,et al .A hardware-friendly method for rate-distortion optimization of HEVC intra coding[C]∥ Proceedings of 2014 International Symposium on VLSI Design,Automation and Test.Hsinchu:IEEE,2014:1-4. |

| 6 | XU Y, HUANG X .Hardware-oriented fast CU size and prediction mode decision algorithm for HEVC intra prediction[C]∥ Proceedings of 2019 IEEE the 5th International Conference for Convergence in Technology.Bombay:IEEE,2019:1-5. |

| 7 | ZHANG Y, LU C .Efficient algorithm adaptations and fully parallel hardware architecture of H.265/HEVC intra encoder[J].IEEE Transactions on Circuits and Systems for Video Technology,2018,29(11):3415-3429. |

| 8 | 杨贺,杨秀芝,陈建 .一种新的基于FPGA的HEVC帧内预测硬件结构[J].福州大学学报(自然科学版),2020,48(3):318-324. |

| YANG He, YANG Xiuzhi, CHEN Jian .A new hardware structure of HEVC intra prediction based on FPGA [J].Journal of Fuzhou University(Natural Science Edition),2020,48(3):318-324. | |

| 9 | MIN B, XU Z, CHEUNG R C C .A fully pipelined hardware architecture for intra prediction of HEVC[J].IEEE Transactions on Circuits and Systems for Video Technology,2016,27(12):2702-2713. |

| 10 | LU W, YU N,NAN J,et al .A hardware structure of HEVC intra prediction[C]∥ Proceedings of 2015 the 2nd International Conference on Information Science and Control Engineering.Shanghai:IEEE,2015:555-559. |

| 11 | CHEN W, HE Q, LI S,et al .Parallel implementation of H.265 intra-frame coding based on FPGA heterogeneous platform[C]∥ Proceedings of 2020 IEEE the 22nd International Conference on High Performance Computing and Communications;IEEE the 18th International Conference on Smart City;IEEE the 6th International Conference on Data Science and Systems. Yanuca Island:IEEE,2020:736-743. |

| 12 | WANG M, WEI H, FANG Y,et al .Fast mode selection algorithm for HEVC intra encoder[C]∥ Proceedings of 2018 IEEE International Conference on Automation,Electronics and Electrical Engineering.Shenyang:IEEE,2018:169-172. |

| 13 | TARIQ J, IJAZ A, ARMGHAN A,et al .HEVC’s intra mode process expedited using Histogram of oriented gradients[J].Journal of Visual Communication and Image Representation,2022,88:103594/1-10. |

| 14 | 杨秀芝,赵敏,施隆照,等 .面向硬件的帧内预测模式选择快速算法与实现[J].计算机辅助设计与图形学学报,2019,31(1):158-164. |

| YANG Xiuzhi, ZHAO Min, SHI Longzhao,et al .Research and implementation of fast algorithm for intra prediction mode selection oriented to hardware[J].Journal of Computer-Aided Design & Computer Graphics,2019,31(1):158-164. | |

| 15 | ATAPATTU S, LIYANAGE N, MENUKA N,et al .Real time all intra HEVC HD encoder on FPGA[C]∥ Proceedings of 2016 IEEE the 27th International Conference on Application-specific Systems,Architectures and Processors.London:IEEE,2016:191-195. |

| 16 | AMISH F, BOURENNANE E .Fully pipelined real time hardware solution for high efficiency video coding (HEVC) intra prediction[J].Journal of Systems Architecture,2016,64:133-147. |

/

| 〈 |

|

〉 |